- Anúncios -

O que significa setting?

O que significa setting? Essa palavra, que pode ser traduzida como "configuração" ou "ambiente", engloba muito mais do que apenas um local físico. Setting é a construção cuidadosa de cada detalhe que compõe uma cena, seja em um livro, filme, ou até mesmo na vida real. É a soma dos elementos visuais, sonoros, emocionais, que transportam o espectador para um…

O que significa tongue?

Você já se perguntou o que significa "tongue" em português? Essa palavra, que literalmente traduzida significa "língua", pode assumir diferentes significados e contextos. Descubra neste artigo o amplo espectro de interpretações desse termo fascinante!

O que significa a palavra abide?

A palavra "abide" tem uma sonoridade misteriosa, como se escondesse segredos antigos. No entanto, sua definição é simples: "abide" significa "permanecer" ou "aguentar" em português. Apesar de sua simplicidade, essa palavra carrega consigo um profundo senso de resistência e determinação. Ao entender seu significado, podemos vislumbrar um mundo repleto de força interior e paciência incansável.

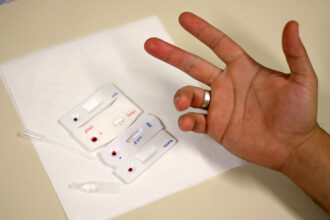

Medicina

O quê significar ser ayurvédico?

O quê significa ser ayurvédico? A resposta a essa pergunta é como…

Create an Amazing Newspaper

Siga-nos

O que significa adição na matemática?

Quando mergulhamos no mundo da matemática, nos deparamos com diferentes termos e…

O que significa dividendo?

Você já se perguntou o que significa dividendo? Essa é uma palavrinha…

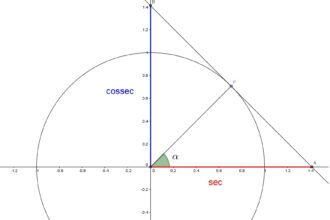

O que significa tangente na matemática?

A tangente, em sua essência matemática, é uma relação misteriosa entre duas…

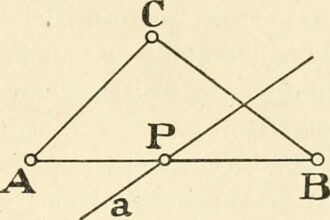

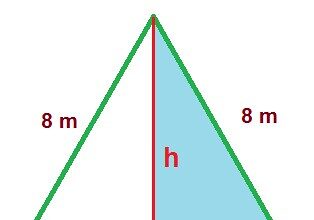

O que significa escaleno?

Escaleno, uma palavra que encerra mistério e equilíbrio. Entre os triângulos, este…

O que significa equilátero?

No mundo da geometria, a palavra "equilátero" evoca harmonia, perfeição e equidade.…

O que significa derivada na matemática?

Derivada na matemática é como uma chave mágica que nos permite desvendar…

O que significa propriedades matemáticas?

Você já se perguntou o que significa propriedades matemáticas? Neste artigo, exploraremos…

O que significa potenciação?

Você provavelmente já se deparou com a potenciação em algum momento da…

Create an Amazing Newspaper

Conteúdo patrocinado

O que significa capitalismo?

O que significa capitalismo? É um conceito que se desdobra em um verdadeiro oceano de interpretações e debates. Desde sua origem na Revolução Industrial até os dias atuais, o capitalismo abrange os pilares da propriedade privada, da livre iniciativa e do mercado competitivo. Mas, será que esse sistema econômico tem se mostrado eficiente e sustentável para todos? Exploraremos essas questões e muito mais neste artigo, mergulhando nas profundezas desse complexo sistema que molda nossa sociedade contemporânea.

O que significa INSS?

INSS, o Instituto Nacional do Seguro Social, é um órgão brasileiro que tem como objetivo garantir proteção social aos cidadãos e promover o bem-estar. O nome pode parecer simples, mas…

Top Autores

Stay Up to Date

Subscribe to our newsletter to get our newest articles instantly!